Documento zippato

Documento PDF

Il transistor JFET

I transistor JFET sono transistor unipolari, in cui, cioè, abbiamo solo correnti di lacune o solo correnti di elettroni.

Il termine JFET sta per junction field effect transistor.

La struttura di principio di un JFET è la seguente

Abbiamo una barretta di silicio drogata in maniera omogenea: se il drogaggio è di tipo n ci troviamo di fronte ad un JFET a canale N, in caso opposto ci troviamo di fronte ad un JFET a canale P. Come si può notare dalla figura, nel JFET a canale N sono realizzate due isole di tipo p, mentre nel JFET a canale P sono realizzate due isole di tipo N.

Al canale sono collegati due elettrodi denominati Source e Drain. Le due isole drogate in maniera diversa dal canale sono collegate a due morsetti detti di Gate. In realtà il dispositivo presenta tre morsetti poiché i due morsetti di gate sono collegati in un unico morsetto di Gate esterno.

Per spiegare la struttura del dispositivo facciamo riferimento al JFET a canale N, poiché il discorso è del tutto equivalente per l’altro tipo di dispositivo.

Supponiamo inizialmente di collegare soltanto una batteria fra Source e Drain. Come potete intuire utilizzando la vostra fervida, incredibile, meravigliosa, straordinaria, incomparabile, spaventosa, stupefacente, ecc. ecc., intelligenza, i nomi dati ai morsetti indicano che vogliamo che si generi una corrente di portatori di carica che nel nostro esempio sono elettroni, che vada dal Source al Drain. Nel nostro esempio dobbiamo necessariamente introdurre una batteria fra Source e Drain con il morsetto positivo collegato al Drain. In sostanza dobbiamo introdurre una tensione VDS>0.

Come si comporta, in tal caso il dispositivo? Facendo riferimento alle vostre meravigliose, cosmiche, oceaniche, universali ecc. ecc. capacità intellettuali spero che vi rendiate conto che ci troviamo di fronte ad una barretta di semiconduttore drogata omogeneamente, per cui ricca di portatori di carica, che si comporta dunque come un corpo conduttore, che offre una resistenza che dipende dalla lunghezza del canale, dalla sua sezione, dalla resistività, cioè dalla ricchezza del drogaggio. Il legame fra la VDS e la corrente di drain ID sarà dunque espresso dalla legge di Ohm. Graficamente tale legame sarà rappresentato da una retta.

Colleghiamo ora una batteria fra Source e Gate, con il positivo verso il Source.

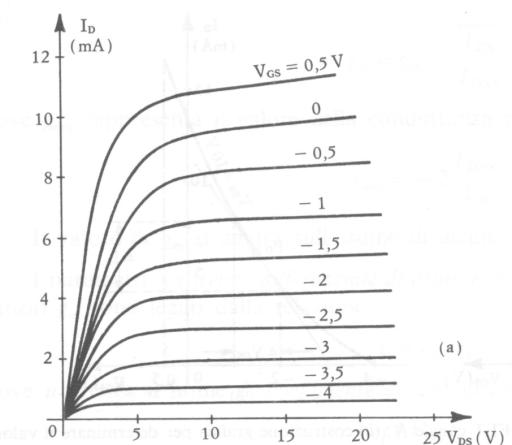

Ponendo la batteria in questo modo, le due giunzioni pn presenti nel dispositivo vengono polarizzate inversamente per cui si creano due zone di svuotamento che penetrano nel canale riducendo la regione in cui si trovano elettroni, sede della corrente. Riducendosi la sezione del canale aumenta la resistenza offerta dal dispositivo, per cui la caratteristica che lega tensione VDS e corrente ID è ancora una retta ma che forma un angolo minore con l’asse delle ascisse. Al crescere del valore assoluto della tensione VGS aumenta ancora la zona di svuotamento, si riduce ancora l’ampiezza del canale e aumenta ancora di più la resistenza offerta dal JFET. Il legame fra VDS e ID, dunque, non è univoco, ma dipende dal valore della VGS .

Possiamo dire dunque che il JFET si comporta come un resistore di cui, però, possiamo modificare la resistenza comandandolo con la tensione VGS.

Questo però, non è sempre vero, ma vale per bassi valori della VDS. Al crescere di tale tensione, infatti, si scopre che le caratteristiche non restano rettilinee ma cominciano ad incurvarsi fino a diventare orizzontali (in termini tecnici si dice che si storzellano).

Per spiegare tale fenomeno, per semplicità consideriamo la caratteristica per VGS=0. Cortocircuitiamo dunque Source e Gate.

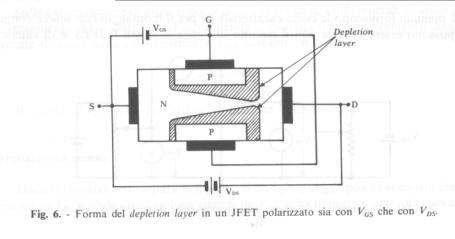

A questo punto consideriamo un punto qualsiasi A nel canale. Questo punto si troverà ad una certa tensione VAS positiva rispetto al Source: ora il fatto che Source e Gate sono cortocircuitati comporta che tale punto A si troverà a tensione positiva anche rispetto al Gate. Questo significa che, anche se non inseriamo una batteria fra Gate e Source, già la VDS fa in modo che i punti del canale si trovino a tensione superiore rispetto al Gate. Inoltre va tenuto presente che, più ci si avvicina al Drain più aumenta la tensione esistente fra i punti del canale e il Source. Quindi più ci si avvicina al Drain e più aumenta la tensione fra i punti del canale e la zona di Gate. In definitiva abbiamo che anche la VDS fa polarizzare inversamente le giunzioni pn creando delle

zone di svuotamento che crescono andando verso il Drain.

Se i valori della VDS sono ancora piccoli, tali zone di svuotamento non sono tali da ridurre significativamente l’ampiezza del canale e il dispositivo mostra una resistenza costante (zona a caratteristica rettilinea). Ma quando la VDS aumenta, le zone di svuotamento che essa crea diminuiscono significativamente l’ampiezza del canale, per cui all’aumentare della tensione, il canale tende a restringersi sempre di più e la sua resistenza comincia ad aumentare (zona in cui la caratteristica si storzella). Come potete intuire utilizzando le vostre fantasmagoriche capacità matematico-filosofiche, esisterà un valore di tensione VDS per il quale le due zone di svuotamento crescono tanto da toccarsi distruggendo completamente il canale: questa tensione è detta tensione di pinch-off ed in corrispondenza di essa la corrente ID diventa quasi costante e la caratteristica diventa quasi orizzontale (in termini tecnici si dice che si corca). Le vostre menti geniali diranno a questo punto: ma se si è distrutto il canale è come se la resistenza fosse diventata infinita, cioè la corrente dovrebbe annullarsi. Tenete presente che, da questo momento in poi ci troviamo in una condizione di equilibrio dinamico. Se, infatti al corrente diminuisse vorrebbe dire che la tensione nel canale dovrebbe diminuire: tenete presente che vale la legge di ohm, per cui nel canale abbiamo una caduta di tensione pari alla resistenza di ogni tratto del canale per la corrente che passa (vedi figura)

se diminuisse la corrente diminuirebbe dunque la tensione lungo il canale, ma poiché source e gate sono sempre cortocircuitati, diminuirebbe anche la tensione fra punti del canale e gate, per cui le zone di svuotamento si ridurrebbero e il canale si riaprirebbe. A questo punto la corrente potrebbe aumentare di nuovo essendosi riaperto il canale, ma ciò comporterebbe un aumento delle cadute di tensione nel canale, e quindi delle tensioni fra canale e gate, con un nuovo aumento dello spessore delle zone di svuotamento,ecc. Insomma la corrente ID non può né aumentare né diminuire per cui diventa quasi costante e dipende debolmente dalla tensione VDS.

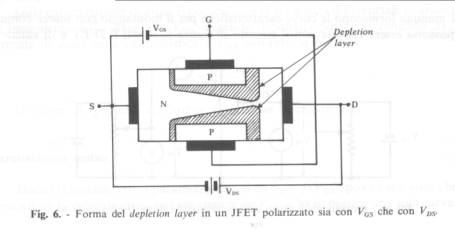

Abbiamo spiegato dunque, perché la caratteristica che lega ID e VDS, per VGS nulla, non è sempre rettilinea. Ma cosa succede quando sono presenti entrambe le batterie?

Nulla di diverso. Si ha una sovrapposizione degli effetti provocati

singolarmente dalle batterie quando agiscono da sole. Si hanno zone di

svuotamento a cuneo che sono più ampie di quelle che provocherebbe la sola VDS,

poiché vi è anche il contributo della VGS.

Notiamo esplicitamente che, come nel caso del BJT, anche il JFET si può montare in più maniere differenti. Se lo montiamo nella maniera seguente

abbiamo il montaggio a source comune che corrisponde al montaggio ad emettitore comune del BJT, ed è utilizzato per fare del JFET un amplificatore di segnali. Notiamo esplicitamente che, in questo montaggio, le grandezze di uscita sono la tensione VDS e la corrente ID, per cui quelle che abbiamo tracciate prima sono le caratteristiche di uscita. Le grandezze di ingresso dovrebbero essere la VGS e la IG. In tal caso, però, non abbiamo una caratteristica di ingresso come nel caso del BJT, poiché la corrente di gate è nulla (per la precisione è una piccolissima corrente dovuta ai portatori di carica minoritari che attraversano la giunzione fra gate e canale), in quanto, come abbiamo implicitamente dimostrato nel corso della trattazione, tale dispositivo va utilizzato tenendo sempre le giunzioni di gate in polarizzazione inversa.