Documento word

Documento pdf

Documento zippato

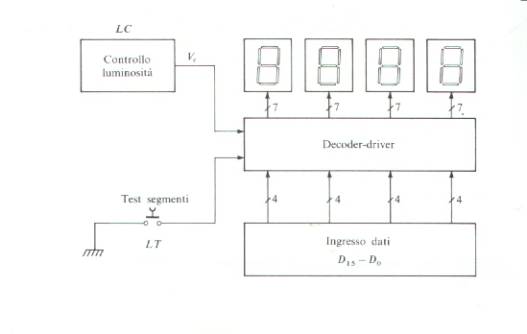

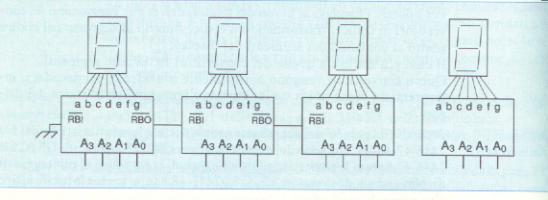

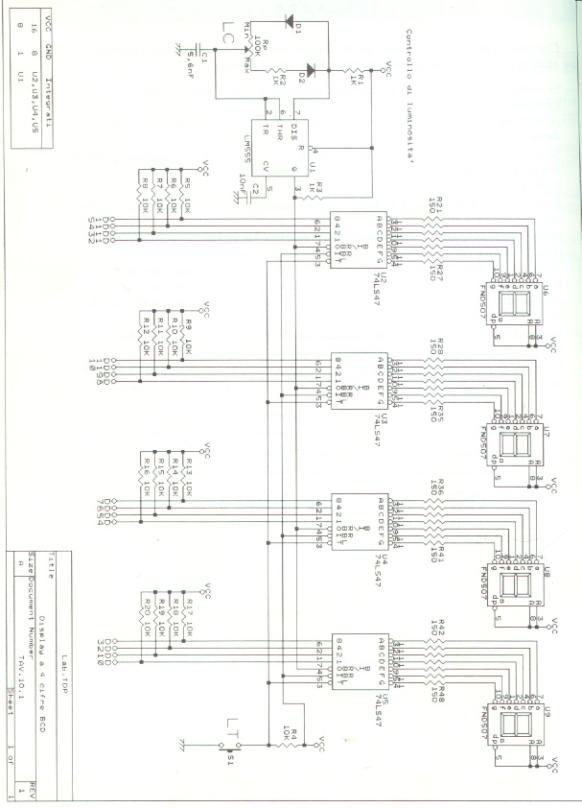

Sistema di visualizzazione a 4 cifre.

Schema a blocchi

Il nostro scopo è quello di costruire un dispositivo rappresentabile dal seguente schema a blocchi

In questo sistema abbiamo 16 ingressi binari. I valori esadecimali assunti da ogni gruppo di quattro bit (o nibble) devono essere visualizzati da un display a sette segmenti. Deve essere poi presente un pulsante detto LT (Lamp Test) che consente di accendere contemporaneamente tutti i Led per testare i display. Il blocco denominato LC è un sistema che deve consentire di variare manualmente la luminosità dei display.

Richiami sui i led e i display.

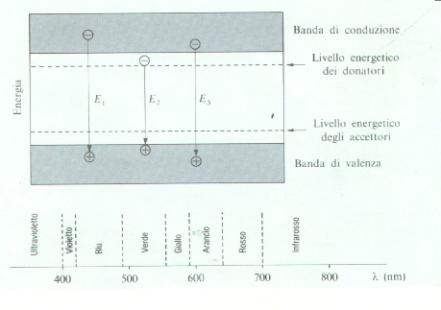

I LED o Light Emitting Diode sono particolari diodi a semiconduttori.

Il semiconduttore utilizzato può essere fosfuro

di gallio o arseniuro

di gallio drogati con zinco

o selenio.

La struttura di principio di diodo

led è identica a quella di un diodo normale. Quando il diodo è polarizzato

direttamente elettroni e lacune si incontrano a cavallo della giunzione e

avviene al ricombinazione. Occorre ora ricordare che un elettrone

libero possiede più energia di un elettrone vincolato in un orbitale.

Quando l’elettrone si ricombina con una lacuna deve dunque cedere l’energia in

più che possiede. Ciò avviene attraverso l’emissione di un fotone.

La meccanica

quantistica dimostra che ciò equivale all’emissione di una radiazione di lunghezza

d’onda ![]() , tale che detta E

l’energia del fotone vale la

relazione

, tale che detta E

l’energia del fotone vale la

relazione

![]()

dove c è la velocità della luce pari a 2,998*108 metri al secondo e h rappresenta la cosiddetta costante di Planck pari a 6,626*10-34 Joule*secondo.

Questo fenomeno avviene in ogni diodo. Nei diodi LED, però, la frequenza delle radiazioni emesse è tale che esse sono visibili all’occhio umano (cioè la lunghezza d’onda è compresa fra 400 e 700 nanometri o miliardesimi di metro)

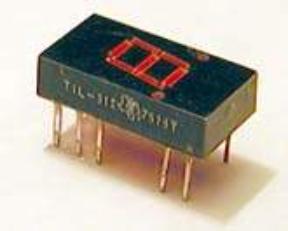

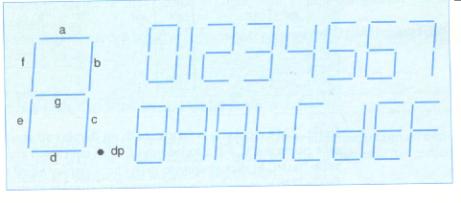

I display sono dispositivi per visualizzare informazioni valori numerici che originano dalle elaborazioni dei vari circuiti digitali

![]()

I più diffusi sono i display a sette segmenti

essi sono costituiti da sette led.

L’accensione dei led giusti consente di comporre tutte le cifre da 0 a 9 e le lettere dell’alfabeto da A ad F, consentendo la visualizzazione di cifre esadecimali.

I led possono essere collegati in una configurazione detta ad anodo comune oppure a catodo comune.

Nel primo caso illustrato dalla figura di sinistra, i led hanno tutti l’anodo collegato alla Vcc. Per accendere un segmento allora dobbiamo polarizzarlo direttamente, portando a zero il segnale collegato al suo catodo, altrimenti esso rimarrà spento. Nell’altra configurazione, i led hanno tutti il catodo in comune. Per accendere un led dobbiamo portare a livello logico alto il segnale corrispondente. Ad esempio, se volgiamo visualizzare il numero 1, dobbiamo far illuminare i segmenti b e c. se il display è a catodo comune, i segnali collegati ai segmenti a, d, e, f, g devono essere a livello basso e i segnali b e c devono essere a livello alto. Nel caso del display ad anodo comune, i segnali collegati ai segmenti a, d, e, f, g devono essere a livello alto e i segnali b e c devono essere a livello basso.

Decoder per display

Abbiamo visto che con un display a sette segmenti, possiamo visualizzare cifre da 0 a F (cioè 15), valori che sono esprimibili mediante combinazioni di quattro bit. Ci si rende conto che, per comandare questi display, occorre un circuito che converta queste combinazioni di quattro bit nei valori che devono assumere i sette segnali che comandano i display. Questa funzione è svolta da opportuni integrati come il 7446.

Questi integrati hanno quattro ingressi (da A0 a A3) cui

vanno collegati i bit da visualizzare e sette uscite che comandano i segmenti del display. Essi hanno le uscite attive

basse per cui possono comandare display ad anodo comune. Essi presentano anche

degli ingressi di controllo: in particolare l’ingresso ![]() ha una doppia

funzione. Usato da solo funziona come Blanking

Input, cioè se posto a livello basso fa in modo che i segmenti si spengano

indipendentemente dai rispettivi segnali di comando. Ad esso si può anche

collegare un segnale ad onda quadra, in modo da fare accendere i segmenti in

maniera intermittente. Se la frequenza è abbastanza alta (dell’ordine dei kHz)

a causa delle proprietà dell’occhio umano (persistenza dell’immagine sulla

retina) non si nota lo spegnimento dei segmenti e l’effetto complessivo è una

variazione della luminosità dei led al variare del duty cicle dell’onda

(maggiore è la percentuale di tempo in cui i led sono accesi e maggiore appare

la loro luminosità).

ha una doppia

funzione. Usato da solo funziona come Blanking

Input, cioè se posto a livello basso fa in modo che i segmenti si spengano

indipendentemente dai rispettivi segnali di comando. Ad esso si può anche

collegare un segnale ad onda quadra, in modo da fare accendere i segmenti in

maniera intermittente. Se la frequenza è abbastanza alta (dell’ordine dei kHz)

a causa delle proprietà dell’occhio umano (persistenza dell’immagine sulla

retina) non si nota lo spegnimento dei segmenti e l’effetto complessivo è una

variazione della luminosità dei led al variare del duty cicle dell’onda

(maggiore è la percentuale di tempo in cui i led sono accesi e maggiore appare

la loro luminosità).

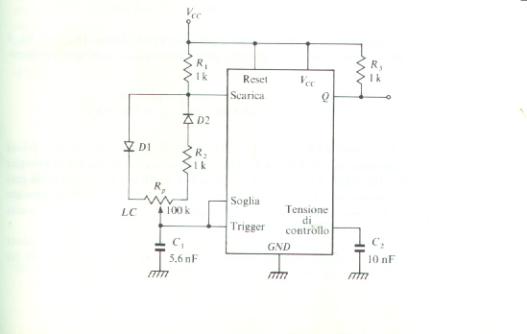

Il progetto

Il progetto complessivo è visualizzato nella figura

seguente. Come si può vedere, abbiamo quattro display comandati dal rispettivo

decoder 7447. per poter variare la luminosità dei display abbiamo collegato i

segnali ![]() di tutti i decoder

all’uscita di un circuito generatore di clock basato sull’integrato NE555.

di tutti i decoder

all’uscita di un circuito generatore di clock basato sull’integrato NE555.

Come sapete grazie alle vostre fantastiche conoscenze, in questo circuito generatore di clock, il tempo in cui l’onda quadra è a livello alto è pari a

Avendo scelto un potenziometro Rp pari a 100 K e un condensatore di valore commerciale 5.6 nF si ha

![]()

Spostando il cursore tutto a sinistra si ha

![]()

mentre con il cursore tutto a destra si ha

![]()

Le resistenze denominate da R21 a R48, sono interposte fra i diodi dei display e le uscite dei decoder driver ed hanno lo scopo di limitare la corrente che fluisce nei led che costituiscono i segmenti dei display. Per ogni segmento potremmo schematizzare la situazione nel modo seguente

Il decoder, per far accendere il segmento, deve portare il suo catodo a massa, per cui la situazione diventa

Per dimensionare la resistenza R occorre tener presente la famosa legge di Ohm generalizzata per cui si ha

VCC = VD

+VR

e ricordare che la tensione ai capi di un diodo led in polarizzazione diretta è un po’ più grande di quella ai capi di un diodo normale e vale circa 1,7 volt. Inoltre la corrente in un diodo led può raggiungere il valore di una ventina di milliampere. Per cui abbiamo

Le resistenze da R5 ad R20 sono resistenze di pull-up (“tira su”: un po’ come i reggiseno). Il loro scopo è di fare in modo che, quando gli ingressi da D0 a D15 non sono utilizzati (cioè in ingresso non vi è alcun segnale), siano portati alla tensione VCC in modo da garantire che i led non si accendano. I valori di queste resistenze devono essere scelti in modo che, quando in ingresso vi sia un valore logico basso o un valore logico alto, in esse non si instaurino correnti tali da cambiare i livelli di tensione voluti sugli ingressi stessi. Per capire meglio questo concetto dobbiamo richiamare alcuni concetti sulle porte logiche

Caratteristica di trasferimento

La caratteristica di trasferimento è un grafico che mostra la relazione che vi è fra le tensioni d’ingresso e di uscita di una porta. Nella figura, ad esempio, è mostrata la curva di trasferimento per una porta NOT che mostra la relazione esistente fra la tensione Vi d’ingresso (riportata sull’asse delle ascisse) e la tensione VO di uscita.

Su tale curva sono indicati dei valori di tensione la cui conoscenza è fondamentale per poter progettare correttamente circuiti digitali.

![]() VIHmin

è il più piccolo valore della tensione d‘ingresso che viene interpretato

correttamente dalla porta come un valore logico 1

VIHmin

è il più piccolo valore della tensione d‘ingresso che viene interpretato

correttamente dalla porta come un valore logico 1

![]() VILmax

è il più grande valore della tensione d’ingresso interpretato correttamente

come un valore logico basso

VILmax

è il più grande valore della tensione d’ingresso interpretato correttamente

come un valore logico basso

I valori di tensioni d’ingresso compresi fra questi due valori appartengono ad una zona d’indeterminazione che va evitata per ottenere un funzionamento corretto dei circuiti digitali.

Abbiamo poi

![]() VOHmin

che è il minimo valore della tensione sull’uscita a livello logico alto

VOHmin

che è il minimo valore della tensione sull’uscita a livello logico alto

![]() VOLmax

che è il massimo valore a livello logico basso

VOLmax

che è il massimo valore a livello logico basso

Per le varie famiglie logiche i livelli di tensione sono i seguenti

|

|

STD |

LS |

S |

ALS |

AS |

HC |

4000 |

|

VIHmin |

2.0 |

2.0 |

2.0 |

2.0 |

2.0 |

3.5 |

3.5 |

|

VILmax |

0.8 |

0.8 |

0.8 |

0.8 |

0.8 |

1.5 |

1.5 |

|

VOHmin |

2.4 |

2.7 |

2.7 |

2.7 |

2.7 |

4.2 |

4.6 |

|

VOLmax |

0.4 |

0.5 |

0.5 |

0.5 |

0.5 |

0.4 |

0.4 |

Questi livelli di tensione sono importanti per stabilire l’immunità al rumore delle porte: occorre ricordare che l’ambiente in cui è immerso il circuito elettronico durante il suo funzionamento è sempre soggetto ad inquinamento elettromagnetico che produce disturbi o rumori elettromagnetici che si sovrappongono in ingresso alla porta ai segnali veri e propri.

Per

fare un esempio, se il segnale d’ingresso assume il valore di 0.4volt e vi è un

disturbo elettromagnetico di +0.5 volt, essi si sommano e la porta ha in ingresso

un segnale complessivo di 0.9 volt (fare attenzione che segnale e disturbo si

sommano algebricamente per cui se hanno lo stesso segno si sommano e se hanno

segno diverso si sottraggono). Il problema è che il segnale modificato dal

rumore può assumere un livello che entra nella fascia di indeterminazione

impedendo alla porta di interpretare in maniera corretta il livello logico di

ingresso. Supponiamo ora di collegare due porte TTL standard.

Per

fare un esempio, se il segnale d’ingresso assume il valore di 0.4volt e vi è un

disturbo elettromagnetico di +0.5 volt, essi si sommano e la porta ha in ingresso

un segnale complessivo di 0.9 volt (fare attenzione che segnale e disturbo si

sommano algebricamente per cui se hanno lo stesso segno si sommano e se hanno

segno diverso si sottraggono). Il problema è che il segnale modificato dal

rumore può assumere un livello che entra nella fascia di indeterminazione

impedendo alla porta di interpretare in maniera corretta il livello logico di

ingresso. Supponiamo ora di collegare due porte TTL standard.

Dalla tabella vediamo che

|

VIHmin |

2.0 |

e

|

VOHmin |

2.4 |

Ciò vuol dire se il segnale d’ingresso alla porta B si mantiene minore o uguale a 2.0 volt esso viene interpretato correttamente come un valore logico zero. Poiché la massima tensione in uscita dalla porta A è di 2.4 volt, se il rumore si somma ad essa non c’è problema (infatti la tensione salirà ancora di più), mentre se il rumore si sottrae alla VIH min si avrà un problema di interpretazione del livello logico se si scende al disotto dei 2 volt. Abbiamo dunque un margine di sicurezza di NMH=VOHmin – VIHmin= 2.4 – 2.0 = 0.4 volt. Questo margine di sicurezza è detto margine di rumore a livello logico alto e ci dice dunque che disturbi sino a 0.4 volt di ampiezza massima non provocano problemi a livello logico alto. Se passiamo a livello logico basso vediamo che

|

VILmax |

0.8 |

e

|

VOLmax |

0.4 |

In questo caso la porta B interpreterà il segnale che si trova sul suo piedino d’ingresso come un livello logico zero se non supera gli 0.8 volt. Poiché la massima tensione in uscita dalla porta A a livello basso è di 0.4 volt, se il rumore non supera gli 0.4 volt tutto va bene e non si entra nella zona di indeterminazione. Anche in questo caso abbiamo un margine di rumore pari a

NML = V ILmax – VOLmax = 0.8 – 0.4 = 0.4 volt

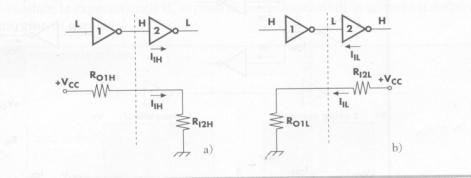

Correnti in una porta

Quando l’uscita di una porta si trova al livello logico alto, si ha la situazione della figura a) per cui la porta 1 si può interpretare come un generatore di tensione che ha una resistenza interna RO1H. Questo generatore eroga una corrente che va in ingresso alla seconda porta, che si può schematizzare con una resistenza. La tensione VOH che troviamo in uscita alla porta 1 dipende dunque dalla corrente erogata. Infatti, applicando i principi di kirchhoff, si avrà che

VOH = VCC – RO1*IOH

Ciò vuol dire che il valore minimo della VOH può essere garantito se la corrente erogata non cresce troppo.

Discorso analogo quando la uscita della porta 1 è a livello logico basso. In tal caso è la porta 2 che manda una corrente alla porta 1 che viene schematizzata con una resistenza. In questo caso il valore massimo di tensione VOLmax può essere garantito se la corrente non cresce troppo poiché

VOLmax = RO1L * IOL

I valori limite delle correnti sono indicati nella seguente tabella

|

|

STD |

LS |

S |

ALS |

AS |

HC |

4000 |

|

IIH (µA) |

40 |

20 |

50 |

20 |

20 |

0.1 |

0.1 |

|

IIL (mA) |

-1.6 |

-0.4 |

-2 |

-0.1 |

-0.5 |

-0.1µA |

-0.1µA |

|

IOH (mA) |

-0.4 |

-0.4 |

-1 |

-0.4 |

-2 |

-4 |

-0.44 |

|

IOL (mA) |

16 |

8 |

20 |

8 |

20 |

4 |

0.44 |

Per convenzione le correnti sono indicate positive se entrano nella porta e negative se escono, per cui la corrente IOL che effettivamente entra nella porta assume valori positivi mentre la IOH che invece esce assume il segno negativo. IL contrario per le correnti d’ingresso.

Resistenze di pull-up

Quando il singolo ingresso D è a livello alto la situazione è la seguente

mentre con D a livello basso abbiamo la seguente situazione

A livello alto tenendo conto che il decoder assorbe una corrente IIH massima di 20 microampere (essendo in tecnologia low schottky), sull’ingresso del decoder si avrà una tensione data da VCC meno la caduta di tensione sulla resistenza di pull up scelta di 10 k per cui

VI = VCC –RIIH = 5 – 20*10-6*104 = 5 – 0.2 = 4.8 V

che supera il valore VIHmin.

Quando si ha in ingresso un livello logico basso il dispositivo di pilotaggio di ingresso assorbe una corrente

![]()

inferiore alla IOLmax per qualsiasi famiglia TTL

Test dei display

Con il pulsante LT premuto vengono posti a zero tutti gli ingressi lamp test dei display provocando l’accensione di tutti i segmenti dei display.