Sistema di rilevamento di 16 temperature con interfacciamento a calcolatore tramite porta parallela

Il progetto utilizzato in questi appunti è tratto dal sito di Vincenzo Villa www.vincenzov.net

Data sheet dei componenti utilizzati

![]() Regolatore di tensione Max 603

Regolatore di tensione Max 603

![]() Amplificatore operazionale OP293

Amplificatore operazionale OP293

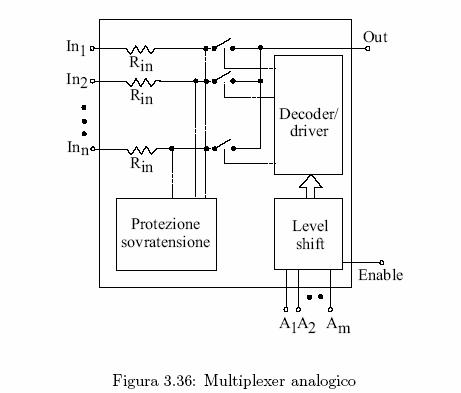

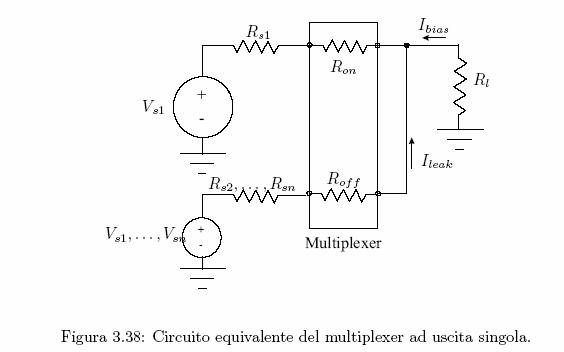

![]() Multiplexer analogico 74HC4067 o 4067

Multiplexer analogico 74HC4067 o 4067

Sistema

di rilevamento di 16 temperature con interfacciamento a calcolatore tramite

porta parallela

La Standard Parallel Port

(SPP).

La Enhanced Parallel Port

(EPP).

La Extended Capabilities Port

(ECP).

Configurare la porta

parallela

Il Serial Peripheral

Interface o SPI

I convertitori

analogico-digitali

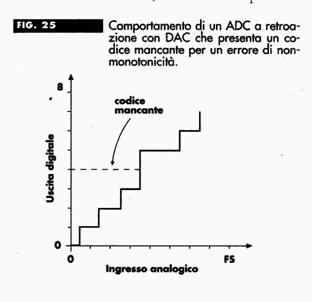

Servo-convertitore o tracking

ADC o ADC ad inseguimento.

Convertitori ad

approssimazioni successive

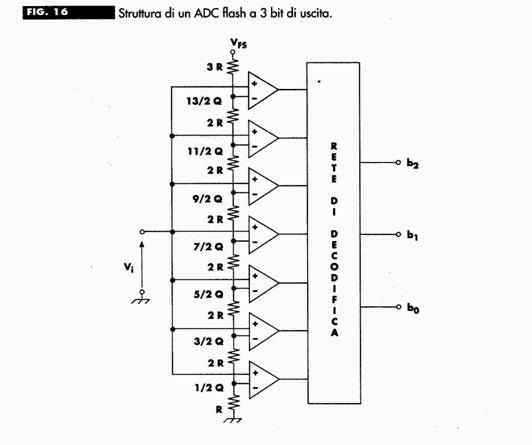

IL convertitore parallelo o

flash

La porta parallela

La porta parallela o centronics è, tra le interfacce disponibili sul personal computer, certamente la più popolare presso gli hobbisti elettronici grazie al fatto che presenta un discreto numero di ingressi ed uscite direttamente compatibili con gli usuali circuiti digitali. Inoltre il suo uso è particolarmente semplice.

Il comune PC in genere possiede una sola porta parallela

a cui possono essere connessi la stampante ed altri dispositivi

"paralleli"(ZIP, scanner, lettori CD esterni…). Essa è spesso

chiamata anche porta LPT (line printer), porta PRN (printer port), porta

stampante oppure ancora interfaccia Centronics.

La porta parallela è facilmente riconoscibile guardando il computer dall'esterno: appare come un connettore a 25 poli DB25 femmina (cioè con 25 fori, disposti due due linee tra di loro sfalsate), posto normalmente sul retro del PC. Non va confusa con la porta seriale che, nei vecchi PC, è costituita da un connettore DB25 maschio (cioè con gli "spilli"). Il connettore in genere installato sulle stampanti (centronics) è a 36 pin ed ha una diversa forma, pur avendo sostanzialmente la stessa funzione; in genere è scomodo da utilizzarsi in quanto ha troppi pin "inutili".

Nella prima fotografia, relativa ad un vecchio PC del 1990 circa si vede in alto il connettore della porta parallela ed in basso i connettori delle due porte seriali, un DB25 ed un DB9.

La seconda fotografia è relativa ad un PC più recente. La porta parallele è quella di color rosso. Gli altri connettori sono la porta joystick e midi (giallo), le due porte seriali a 9 pin, i tre connettori circolari audio (in basso sulla destra), i due connettori USB (sulla sinistra, uno è in parte nascosto) e i due connettori per la tastiera e il mouse (verdi e viola, con i cavi collegati).

Nella fotografia: sulla sinistra un cavo maschio-maschio (i due connettori sono identici), un normale cavo centronics per il collegamento della stampante e, in primo piano, l'adattatore che converte un connettore maschio DB25 in un connettore femmina.

I tipi di porta parallela

Nel tempo la porta parallela montata nel PC si è evoluta anche se, con qualche eccezione, si è mantenuta la compatibilità con i primi modelli: questo significa che tutti i circuiti progettati per essere collegati alla porta parallela del primo PC-XT IBM possono, almeno in teoria, funzionare anche con un moderno P4.

Molti costruttori hanno in passato hanno apportato modifiche e miglioramenti allo standard SPP originario spesso senza porre attenzione alla compatibilità con i modelli di altri produttori: ciò ha reso inutilizzabili sulla generalità dei PC le caratteristiche avanzate disponibili solo per alcune porte parallele.

Le categorie che comprendono tutte le porte "moderne" sono sostanzialmente tre:

Tutti questi modi di funzionamento sono stati normati nello standard IEEE 1284 del 1994

Configurare la porta parallela

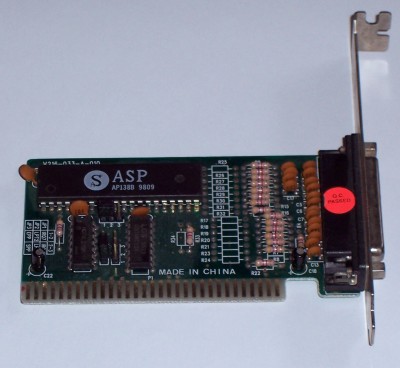

Se il PC è piuttosto vecchio (diciamo fino ad un 486 antecedente al 1995) e la porta parallela è installata su una scheda connessa al bus ISA o VL-bus, molto probabilmente la porta è una SPP e quindi non necessita di alcuna configurazione. In genere la stessa scheda che ospita il connettore stampante ha anche la funzione di controller per i dischi e le porte seriali o, in macchine molto vecchie, di scheda video.

Se la porta è costituita da un chip installato sulla scheda madre in genere è configurabile per alcuni o tutti i modi previsti dalla norma IEEE 1284. Per far ciò è necessario, prima della fase di boot, accedere al menu di configurazione dei parametri del BIOS e cercare alla voce integrated peripherals o simili. Per gli scopi che si vogliono raggiungere la porta va configurata come normal oppure centronics oppure default oppure ancora printer mode, tutti termini sostanzialmente equivalenti. Se previsto è anche possibile selezionare il modo bi-directional oppure EPP.

Se la porta è installata su una piccola scheda aggiuntiva, a volte è disponibile un jumper che permette di configurare la porta come SPP o EPP, oppure il produttore fornisce un software di configurazione.

Qui sopra, l'immagine della classica scheda parallela aggiuntiva su bus ISA.

La scheda va installata in uno slot libero, previa configurazione di alcuni jumper:

LPT1, LPT2 o, in alcuni casi, LPT3. Ovviamente occorre evitare la prima opzione se è già presente la porta parallela principale (cosa quasi sempre vera).

IR5 o IRQ7. Se non sapete cosa fare è opportuno non selezionare nessuno di questi jumper perché, nei PC datati normalmente configurati vi è penuria di interrupt.

Modo SPP o EPP o ancora (più raramente) ECP, quando disponibili. Il modo EPP è più generale e quindi vi consiglio di attivarlo anche nel caso in cui vogliate realizzare circuiti basati sulle idee presentate in questo tutorial.

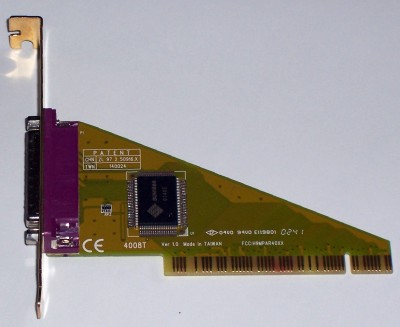

Purtroppo molti PC recenti non dispongono del vecchio bus

ISA, sostituito dal più performante PCI. Sono comunque disponibili anche schede

per PCI come quella riportata nella fotografia seguente, in genere più costose

ma anche più veloci.

Un problema che spesso si presenta con le schede PCI deriva dal fatto che non sono presenti jumper di configurazione ma per la configurazione occorre dipendere dai meccanismi di plug&play del BIOS e del sistema operativo o dai driver forniti dal costruttore (quando presenti!). Occorre anche dire che spesso i chip usati non sono documentati sulla rete Nei PC moderni la porta parallela è gestita da un chip che controlla anche altre interfacce (seriali, dischi...), direttamente saldato sulla scheda madre. In caso di errori nell'uso dell'interfaccia parallela si possono causare guasti fisici irreversibili che si ripercuotono sul funzionamento di tutto il PC. Il chip non è in genere sostituibile e ciò causa la necessità di dover cambiare tutta la scheda madre.

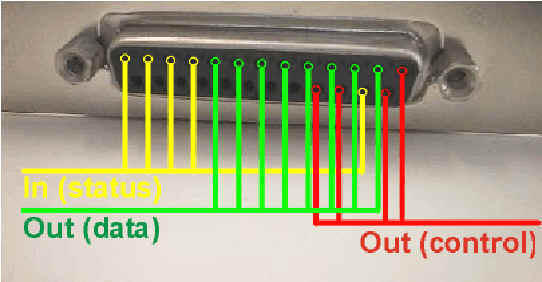

L'assegnazione dei pin

Complessivamente sono disponibili sul connettore della porta parallela 12 bit per l'output e 5 per l'input. Gli ingressi e le uscite sono TTL compatibili (alcuni possono essere a collettore aperto, in genere con resistore di pull-up integrato all'interno del PC) anche se le tensioni e le correnti effettivamente disponibili sono piuttosto variabili in funzione delle tecnologie impiegate per la costruzione della porta.

Su molti PC un uno logico appare come una tensione molto vicina ai 5V, uno zero come 0V (a vuoto). Le correnti disponibili sono in genere di almeno 5 mA sia di sink (cioè quando è il pin ad assorbire corrente) che di source (quando è il pin ad erogare corrente) ma spesso molto di più (anche 50 mA e più). Non si tratta però di una regola: in genere deve essere interpretato come uno logico qualunque tensione superiore ai 2V e come zero logico qualunque tensione inferiore a 0.8V. Inoltre si potrebbe ritenere che la corrente assorbita da un'uscita (Isink) sia maggiore, anche di molto, di quella erogata (Isource).

E' quindi buona norma progettare circuiti che riescano a gestire correttamente segnali che rappresentano l'uno logico sia con i 2V sia con i 5V (quali per esempio i TTL, gli HCT o gli HC con resistore di pull-up. E' anche opportuno evitare correnti in ingresso o uscita superiori a qualche mA.

La seguente tabella riporta l'assegnazione dei pin (sia sul connettore DB25 che su quello Centronics), il loro nome, la direzione (Out significa che il PC invia il bit alla periferica) ed il nome del registro utilizzato per controllarli.

|

Pin DB25 |

Pin centronics |

Nome |

Direzione |

Registro |

|

1 |

1 |

Strobe |

Out * |

Control |

|

2 |

2 |

Data 0 |

Out |

Data |

|

3 |

3 |

Data 1 |

Out |

Data |

|

4 |

4 |

Data 2 |

Out |

Data |

|

5 |

5 |

Data 3 |

Out |

Data |

|

6 |

6 |

Data 4 |

Out |

Data |

|

7 |

7 |

Data 5 |

Out |

Data |

|

8 |

8 |

Data 6 |

Out |

Data |

|

9 |

9 |

Data 7 |

Out |

Data |

|

10 |

10 |

Ack |

In |

Status |

|

11 |

11 |

Busy |

In |

Status |

|

12 |

12 |

Paper Out |

In |

Status |

|

13 |

13 |

Select |

In |

Status |

|

14 |

14 |

Linefeed |

Out * |

Control |

|

15 |

32 |

Error |

In |

Status |

|

16 |

31 |

Inizialize |

Out * |

Control |

|

17 |

36 |

Select-in |

Out * |

Control |

|

18-25 |

19-30, 33 |

Massa |

- |

- |

|

- |

18, 35 |

+ 5V (Rpu) |

- |

- |

|

- |

14, 34 |

Non usato |

- |

- |

I pin di uscita evidenziati da un * sono utilizzabili

anche come ingresso ma solo su alcune porte. In questo caso si tratta di

un’uscita a collettore aperto (open collector).

Alcuni dei pin del connettore Centronics a 36 pin non sono presenti sul connettore a 25 pin.

Realizzando un circuito connesso alla porta parallela è opportuno collegare tutti i fili di massa, sia per semplificare il layout del circuito stampato sia per diminuire gli eventuali disturbi.

L'immagine seguente evidenzia i pin di uscita con l'indicazione dei relativi registri, visti dal connettore del PC. I pin non indicati sono tutti connessi a massa.

La porta EPP

Lo standard EPP 1.7 fu originariamente definito da un

consorzio costituito da Intel, Xircom e Zenith ed in seguito recepito, con

qualche variazione, della norma IEEE 1284 come EPP 1.9.

Diverse sono le caratteristiche interessanti della EPP:

Permette lo scambio bidirezionale di dati senza i problemi di compatibilità della SPP

È sufficientemente veloce, potendo garantire prestazioni confrontabili con quelle del bus ISA. Normalmente ha la stessa velocità della parallela ECP ed è decisamente più veloce della SPP. In funzione del tipo di chip utilizzato per costruirla e della connessione al bus di sistema (ma sostanzialmente indipendentemente dal processore, se questo è abbastanza moderno) la velocità può variare da 500 kilobyte a 2 megabyte al secondo

È più semplice da gestire rispetto alla ECP in quanto non richiede una particolare "intelligenza" alle periferiche né l'uso di driver particolarmente complessi sul PC. Infatti la comunicazione è completamente controllata dall'hardware attraverso semplici istruzioni di I/O anche senza l'uso di interrupt o DMA.

In genere tutte le porte parallele recenti sono

EPP-compatibili anche se occorre impostare correttamente questa modalità di

funzionamento agendo sui parametri del BIOS o posizionando un ponticello. Se la

porta permette la configurazione come EPP 1.7 oppure EPP 1.9, si consiglia la

seconda opzione.

I segnali

La porta EPP utilizza gli stessi connettori e segnali della porta Centronics; ne ridefinisce però i nomi e la funzione, secondo la seguente tabella.

|

Pin |

Nome SPP |

Nome EPP |

Direzione |

Funzione

EPP |

|

1 |

Strobe |

nWRITE |

Out |

Questo

segnale basso indica una scrittura |

|

2 |

Data 0 |

PD 0 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

3 |

Data 1 |

PD 1 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

4 |

Data 2 |

PD 2 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

5 |

Data 3 |

PD 3 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

6 |

Data 4 |

PD 4 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

7 |

Data 5 |

PD 5 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

8 |

Data 6 |

PD 6 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

9 |

Data 7 |

PD 7 |

Bidirezionale |

Trasporta

dati e indirizzi |

|

10 |

Ack |

Interrupt |

In |

Se

abilitato, genera un interrupt sul fronte di salita |

|

11 |

Busy |

nWAIT |

In |

Usato per la

sincronizzazione. |

|

12 |

Paper Out |

- |

In |

Non usato |

|

13 |

Select |

- |

In |

Non usato |

|

14 |

Linefeed |

nDSTRB |

Out |

Quando basso

indica un trasferimento di dati |

|

15 |

Error |

. |

In |

Non usato |

|

16 |

Inizialize |

Reset |

Out |

Attivo

basso, resetta le periferiche |

|

17 |

Select in |

nASTRB |

Out |

Quando basso

indica un trasferimento di indirizzi |

|

18-25 |

Massa |

Massa |

|

|

La numerazione dei pin è relativa al connettore femmina

DB25 presente sul retro del PC. Per alcuni pin della modalità EPP è indicato il

nome premettendo la lettera "n" minuscola (per esempio nASTRB) per

indicare che è attivo basso; a volte lo stesso pin è indicato senza tale

prefisso oppure con un segmento al disopra (qualunque sia la convenzione usata

non vi sono però modifiche ai livelli logici ed i diagrammi temporali indicati

sono quelle "fisicamente" presenti).

Come si nota tre pin di ingresso non sono usati nello standard EPP e quindi possono essere gestiti direttamente dal programma, attraverso le stesse tecniche della porta SPP. Tutti gli altri segnali sono gestiti direttamente dall'HW della porta parallela anche se rimangono comunque disponibili per il controllo via SW secondo le modalità SPP. Ad esclusione dei tre segnali di ingresso non utilizzati non è però consigliabile un utilizzo contemporaneo della modalità EPP e SPP.

I registri EPP

La gestione della EPP avviene attraverso otto registri consecutivi, ciascuno formato da otto bit, presentati nella tabella seguente. Con Base di intende l'indirizzo di base della porta parallela, in genere 0x378 oppure 0x278. Si noti che la porta EPP non può avere indirizzo 0x3BC, corrispondente nella nomenclatura DOS a LPT3.

|

Indirizzo |

Nome |

R/W |

|

Base + 0 |

SPP data

port |

W |

|

Base + 1 |

SPP status

port |

R |

|

Base + 2 |

SPP control

port |

W |

|

Base + 3 |

EPP Address

port |

R/W |

|

Base + 4 |

EPP data

port |

R/W |

|

Base + 5 |

EPP dataport

- 16 bit |

R/W |

|

Base + 6 |

EPP dataport

- 32 bit |

R/W |

|

Base + 7 |

EPP dataport

- 32 bit |

R/W |

Le modalità a 16 e 32 bit non sono supportate da tutte le

parallele EPP: in questo caso i registri corrispondenti non sono definiti.

Come riportato nella tabella i primi tre registri sono sostanzialmente identici sia come nome che come funzione ai registri della SPP e non verranno quindi qui descritti. Questo permette di usare una porta EPP in tutte le applicazioni in cui è richiesta una porta SPP, senza alcuna modifica all'HW o al SW. L'unico problema si può eventualmente presentare qualora si vogliano sfruttare alcune caratteristiche elettriche della SPP, quale la presenza di pin a collettore aperto.

La scrittura di un dato

Come già anticipato nella precedente tabella gli otto pin PD0... 7 permettono il trasporto bidirezionale sia di indirizzi che di dati, ovviamente in tempi diversi.

La sincronizzazione del trasferimento è realizzata attraverso una coppia di segnali che devono essere attivati alternativamente da trasmettitore e ricevitore, secondo uno schema detto "intelocking handshakes". Ciò permette di adeguare la velocità al dispositivo più lento tra quelli collegati.

Il registro Base+4 (Data port) permette di scrivere (o di leggere) un dato sui pin della LPT, semplicemente facendo una singola operazione di scrittura (o lettura).

Di seguito si riporta il diagramma temporale semplificato con l'andamento dei segnali nel caso di scrittura di un dato (cioè un byte è generato dal PC e ricevuto dalla periferica). In verde sono indicati i segnali pilotati dal PC, in rosso quelli pilotati dalla periferica:

Il ciclo inizia con la scrittura da parte del processore di un byte nel registro Base+4 (ciclo generato dall'esecuzione di un a singola operazione di I/O e quindi legato alle variazioni dei segnali interni al PC IOCHRDY, WR e D0..D7, non indicati nel diagramma temporale in quanto non disponibili sul connettore EPP)

nWRITE diventa basso, per indicare un'operazione di scrittura. Questa fase inizia nella EPP 1.9 solo se nWAIT è tenuto basso dalla periferica (come indicato nel diagramma); altrimenti la sequenza si sospende e riprende sul fronte di discesa di nWAIT

Sono posti sui pin PD0…PD7 i dati scritti nel registro

nDSTRB diventa basso per indicare un trasferimento di dati. Queste tre ultime operazioni sono, se nWAIT è basso, praticamente contemporanee, come rappresentato nel diagramma temporale

Il PC attende che nWAIT, generato dalla periferica, diventi alto. Tale evento deve avvenire entro qualche microsecondo. In questo momento termina l'esecuzione dell'operazione di scrittura da parte del processore che può riprendere l'esecuzione del programma temporaneamente sospeso.

E' disattiva nDSTRB

nWRITE diventa alto (cioè inattivo)

I dati presenti su PD0... PD7 non sono più validi. Non è specificato cosa succede: da una serie di informazioni sembra che, a seconda del chip utilizzato, non si hanno cambiamenti oppure viene generato il byte precedentemente scritto in Base+0 oppure ancora i pin sono posti in alta impedenza. Il consiglio è quello di non fare nessun affidamento sullo stato assunto dopo la disattivazione di nWRITE.

Alcune osservazioni:

Tutta la sequenza è realizzata dall'HW: il software deve limitarsi alla scrittura di un singolo byte nel registro opportuno. Il tempo impiegato potrebbe però essere maggiore di quello richiesto da una semplice operazione di I/O perché è previsto l'inserimento di stati d'attesa fino al termine del ciclo, in dipendenza del segnale generato dalla periferica. Ciò permette alla periferica di acquisire il dato lentamente, sospendendo il programma.

Per acquisire il dato presente sul bus una periferica veloce (per esempio un flip-flop edge-triggered) potrebbe utilizzare il fronte di salita di nDSTRB (o di nWait): infatti i dati permangono validi ancora per un tempo di qualche decina di ns, adeguato a garantire il tempo di hold richiesto dai normali circuiti integrati digitali.

Potrebbe invece essere opportuno utilizzare il livello basso o il fronte di discesa di nDSTRB nel caso in cui la periferica sia costituita da un microcontrollore (il ritardo tra l'attivazione di nDSTRB e la validità dei dati è limitato, in funzione del chip utilizzato, a qualche decina di ns ma spesso è addirittura negativo).

Se si utilizza

Se si utilizza

Qualora la periferica non dovesse alzare il segnale di nWAIT entro un tempo "ragionevole", il ciclo viene interrotto ed il timeout segnalato come descritto più avanti.

Il punto 7 dell'elenco precedente si verifica solo se non ci sono altre operazioni di scrittura sulla porta EPP ancora pendenti. In caso contrario nWRITE rimane attivo ed inizia un nuovo ciclo.

La scrittura di un indirizzo

Il ciclo per la scrittura di un indirizzo è sostanzialmente identico alla scrittura di un dato. Le differenze sono solo due:

Il software deve scrivere nel registro Base+3 invece che in Base+4

Il segnale coinvolto non è nDSTRB ma nASTRB

Le altre operazioni, incluse le temporizzazioni ed i timeout, rimangono invariate.

Occorre notare che il termine "indirizzo" oppure "dato" è puramente convenzionale e nulla impedisce di utilizzarli come dato1 e dato2, se nella specifica applicazione hanno questa funzione.

La lettura di un dato o di un indirizzo

La porta EPP gestisce in modo automatico anche il transito di dati ed indirizzi da periferica a PC.

Il ciclo inizia con la lettura da parte del processore del registro Base+4 (oppure base+3 nel caso di lettura di un indirizzo). I segnali interni coinvolti sono, al solito, D0... D7, RD e IOCHRDY e non indicati nello schema semplificato

nDSTRB (oppure nASTRB nel caso di lettura di un indirizzo) diventa basso. Notare che nWRITE rimane alto, cioè inattivo. Anche in questo caso il ciclo inizia nel caso della EPP 1.9 solo se nWAIT è mantenuto basso dalla periferica

La periferica deve mandare sul bus PD0…PD7 i dati (o gli indirizzi). In realtà la periferica può impostare PD0…PD7 in un momento qualunque antecedente questo istante

La periferica deve alzare il pin nWAIT.

Il PC acquisisce il dato da PD0…PD7 in corrispondenza del fronte di salita di nDSTRB (oppure nASTRB).

Il PC pone alto nDSTRB (o nASTRB) e il ciclo termina. I buffer della porta EPP rimangono nello stato di alta impedenza (anche se non tutte le fonti affermano esplicitamente ciò)

La periferica deve porre nWAIT basso prima dell'inizio del ciclo successivo

È necessario che, in corrispondenza la disattivazione di nDSTRB (oppure di nASTRB) siano mantenuti stabili i pin PD0...7 al fine di rispettare i tempi di set-up e di hold della porta: per sicurezza è opportuno che la periferica mantenga i dati stabili per qualche centinaio di ns nell'intorno del fronte di nDSTRB .

Un esempio reale

Nella figura seguente sono riportate le temporizzazioni dettagliate della porta EPP PC87307VUL prodotta da National Semiconductor (http://www.national.com) e ampiamente usato in molti PC. Tale grafico è utilizzabile per la progettazione anche se occorre notare che non si tratta dello standard ufficiale ma solo di un'implementazione relativa ad uno specifico chip.

Accanto ai segnali riportati anche nei precedenti diagrammi semplificati sono presenti anche alcuni segnali interni al PC (WR, RD, D0... 7, IOCHRDY, ZWS), utili per comprendere nel dettaglio il funzionamento del chip ma non necessari per la progettazione di periferiche esterne.

Nel diagramma temporale è rappresentata un'operazione di scrittura seguita da una di lettura. Dallo stato del segnale nWAIT all'inizio del ciclo si vede che la rappresentazione grafica è relativa alla EPP 1.7, come del resto chiarito dalla nota 1.

|

Simbolo |

Parametro |

Condizioni |

Min |

Max |

Unità |

|

tWW |

Tempo tra i fronti di WR (interno) e di nWRITE (1) |

|

|

45 |

ns |

|

tWST |

Tempo tra i fronti di WR (interno) e di nDSTRB (o

nASTRB) (2) |

EPP 1.7 |

|

45 |

ns |

|

EPP 1.9 (1) |

|

65 |

ns |

||

|

tWEST |

Tempo tra l'attivazione di nWRITE e di nDSTRB (o

nASTRB) |

EPP 1.7 |

0 |

|

ns |

|

EPP 1.9 |

10 |

|

ns |

||

|

tWPDh |

Tempo di hold di PD0...PD7 dopo che nDSTRB (o nASTRB)

diviene inattivo |

|

50 |

|

ns |

|

tHRW |

Tempo tra l'attivazione di nWAIT e IOCHRDY (3) |

EPP 1.7 |

|

40 |

|

|

tWPDS |

PD0...PD7 validi dopo che nWRITE diviene attivo |

|

|

15 |

ns |

|

tEPDW |

Tempo di validità di PD0...PD7 |

|

80 |

|

ns |

|

tEPDh |

Validità di PD0...PD7 dopo nDSTRB o nASTRB |

|

0 |

|

ns |

(1) I tempi tWW e tWST sono, nel caso della EPP 1.9, relativi al fronte di WR solo se nWAIT è basso. Altrimenti sono misurati rispetto all'istante in cui nWAIT diviene basso.

(2) E' garantito che nWRITE non passi da basso ad alto prima di nDSTRB (o nASTRB)

(3) Nel caso di EPP 1.9, tempo tra l'attivazione di nRD o nWR e IOCHRDY

Il tempo impiegato dalla porta EPP per completare un ciclo di scrittura o di lettura dipende sostanzialmente dal tempo che la periferica impiega per gestire il pin nWRITE. E' infatti secondario il tipo di chip utilizzato, il tipo di processore e, anche se in misura minore, il tipo di bus con cui la porta EPP è collegata al processore.

Il pin nWRITE interviene direttamente sul segnale IOCHRDY interno al computer che ha lo scopo si sospendere l'esecuzione dell'istruzione di I/O fino al suo completamento, inserendo un certo numero di cicli di ritardo. Si noti che tale sospensione avviene all'interno di un'operazione elementare e questo blocca completamente l'hardware del processore, rendendo impossibile la prosecuzione del programma o l'intervento del sistema operativo, qualunque esso sia. Questo meccanismo porterebbe quindi ad un blocco irreversibile dell'intero computer se, per esempio, nessuna periferica fosse collegata alla porta EPP...

La soluzione è costituita da una sorta di watchdog (cane da guardia) che rileva la situazione appena descritta ed interrompe la sospensione del processore intervenendo direttamente sull'hardware sbloccando il segnale IOCHRDY dopo alcuni microsecondi di inattività. Questo errore è segnalato attraverso l'uso del bit 0 del registro di stato (indirizzo Base+1): se tale bit vale 0 non vi sono stati errori, se vale 1 il ciclo non si è potuto completare a causa di un timeout.

E' opportuno verificare regolarmente questo bit se si utilizza la modalità EPP. Si noti che in caso di errore il SW deve esplicitamente azzerare questo bit altrimenti anche tutte le operazioni successive genereranno a loro volta un timeout.

La lettura/scrittura di dati a 16 e 32 bit

Alcune parallele EPP supportano il trasferimento di dati a 16 e 32 bit. Per fare ciò è sufficiente scrivere (o leggere) una word (16 bit) o una double word (32 bit) nel registro base+4; la porta provvederà a convertire quest'unica scrittura (o lettura) in due o quattro cicli EPP. Il vantaggio è costituito dal fatto che il processore esegue più velocemente la scrittura o la lettura, eseguendo una sola operazione di I/O invece di due o quattro.

Non tutte le porte parallele EPP supportano tale metodo e ciò limita la portabilità tra macchine diverse di questa tecnica.

Per gli indirizzi è previsto solo il trasferimento di 8 bit.

La preparazione della porta

Prima di utilizzare la porta in modalità EPP è opportuno eseguire due operazioni:

La porta EPP nel suo stato inattivo ha i segnali nDSTRB, nASTRB e nWRITE alti. In alcune porte, prima dell'inizio del primo ciclo di I/O EPP, potrebbe essere necessario porli manualmente in questo stato scrivendo direttamente nel registro di controllo SPP. Nel caso di porte che non richiedono questa impostazione, l'operazione è inutile ma assolutamente non dannosa, né per la configurazione della porta né per la periferica

Alcune porte non possono iniziare un ciclo EPP se il buffer bidirezionale della porta SPP è stato configurato in ingresso attraverso il settaggio del bit 5 del registro di controllo

Per questi motivi è opportuno porre sul registro di controllo il byte 00000100b attraverso l'istruzione:

outportb (control_reg, 0x04);

Questa operazione è necessaria una sola volta, all'inizio del programma: nelle successive operazioni di I/O il controllo di questi segnali è gestito unicamente dall'HW. La successiva gestione via SW potrebbe addirittura creare problemi e pertanto vivamente sconsigliata.

Prima dell'utilizzo è ovviamente necessario impostare la porta (attraverso il settaggio dei parametri del BIOS o un apposito jumper) come EPP 1.7, 1.9 oppure EPP/SPP.

Il Serial Peripheral Interface o SPI

Il Serial Peripheral Interface o SPI è un bus standard di comunicazione seriale ideato dalla Motorola e sviluppato, in una sua variante, anche dalla National Semiconductor con il nome di bus Microwire.

Il bus SPI è un bus sincrono e full-duplex ideale in tutte quelle situazioni in cui un dispositivo master deve interfacciarsi a diversi dispositivi slave e con loro dialogare in modo efficace e performante.

Esso si basa su 4 segnali:

SCLK Serial Clock

SDI Serial Data Input

SDO Serial Data Output

CS Chip Select

Di questi il Chip Select non è indispensabile in tutte le situazioni.

Il segnale SCLK è il clock seriale che scandisce gli istanti di emissione e di lettura dei bit sulle linee di dato. È un segnale emesso dal master ed è quindi quest'ultimo a richiedere di volta in volta la trasmissione di una parola.

Il segnale SDI è la linea attraverso cui il dispositivo (master o slave) riceve il dato seriale emesso dalla controparte. Corrispondentemente, il dispositivo emette, con la stessa cadenza, il suo output ponendo il dato sulla linea SDO (linea di output di dato).

La linea CS è dedicata all'abilitazione del dispositivo slave da parte del master che così facendo abilita l'uno o l'altro dispositivo slave che si affaccia al bus ad intrattenere una trasmissione. La linea CS, normalmente attiva bassa, in caso di disabilitazione lascia il dispositivo slave con uscita in alta impedenza e quindi isolato completamente dal bus indifferentemente dall'esistenza del segnale di clock.

Il numero di dispositivi slave che si possono connettere al bus è limitato esclusivamente dal numero di possibili linee di chip select gestibili dal dispositivo master. La frequenza di clock, e di conseguenza la velocità del bus, può raggiungere, con questo standard, livelli anche elevati nell'ordine delle decine di MHz ed anche oltre.

Come avviene la comunicazione

La trasmissione dei dati sul bus SPI si basa sul funzionamento dei registri a scorrimento (shift register). Ogni dispositivo sia master che slave è dotato di un registro a scorrimento interno i cui bit vengono emessi e, contemporaneamente, immessi, rispettivamente, tramite l'uscita SDO e l'ingresso SDI. Il registro può avere dimensione arbitraria (ma uguale per dispositivo master e slave) anche se usualmente ha la dimensione di 8 bit.

Il registro a scorrimento è un'interfaccia completa mediante la quale vengono impartiti comandi e trasmessi dati che arrivano in modo seriale ma che internamente sono prelevati, a fine trasmissione, in modo parallelo.

Ad ogni impulso di clock i dispositivi che stanno comunicando sulle linee del bus emettono un bit dal loro registro interno rimpiazzandolo con un bit emesso dall'altro interlocutore. La sincronizzazione è fatta sui fronti di clock di salita o di discesa regolata da 2 parametri impostabili: CKP e CKE.

CKP regola la polarità del clock ovvero discrimina lo stato normale di riposo cui si porta la linea di clock quando non è attiva. Quando CKP è impostato a 0 il clock, nel suo stato di riposo, si porta a livello logico basso, viceversa si porta a livello logico alto, durante il tempo di inattività, se CKP è impostato ad 1.

CKE regola il fronte di clock in cui il ricevente

campiona il segnale in ingresso. Se CKP=0 allora con CKE possiamo scegliere di

campionare il dato sul fronte di discesa del segnale di clock, impostando

CKE=0, oppure sul fronte di salita, impostando CKE ad

Queste opzioni, in genere, sono impostabili sul dispositivo master e permettono di adattarlo a tutte le possibili varianti di dispositivi slave che normalmente, invece, vengono progettati per avere uno dei 4 modi di comunicazione possibili (tutte le combinazioni di CKE e CKP).

Le modalità di funzionamento più spesso utilizzate dai dispositivi in commercio sono quelle con CKE=CKP=0 e con CKE=CKP=1.

Il dato di output è emesso sempre in corrispondenza della prima transizione del clock.

La comunicazione viene intrapresa sempre su iniziativa del dispositivo master che abilita lo slave tramite CS e successivamente impone il clock sulla linea dedicata. Con questa procedura ha inizio lo scambio dei bit tra i due registri. Alla fine di ogni parola trasmessa il contenuto del registro dello slave sarà passato al master e viceversa. Con opportune parole identificative si possono inviare comandi al dispositivo ricevente che potrà effettuare l'elaborazione assegnata ponendo quindi nel suo shift-register il dato richiesto che al prossimo ciclo di trasmissione verrà trasmesso al richiedente.

I convertitori analogico-digitali

Un convertitore analogico digitale ha la funzione inversa a quella di un convertitore DAC, poiché il suo scopo è quello di permettere ad un sistema a microprocessore di acquisire informazioni su grandezze analogiche, trasformandole in stringhe di bit corrispondenti. Quindi un ADC accetta in ingresso una grandezza analogica, per esempio una tensione, e restituisce in uscita un numero espresso in forma binaria secondo un opportuno codice, che rappresenta la grandezza analogica in ingresso.

Nella conversione analogico/digitale è ineliminabile la perdita d’informazione. Infatti una grandezza analogica varia con continuità all’interno di un range quindi assume infiniti valori mentre la grandezza numerica in uscita può assumere un numero finito di valori in dipendenza del numero di bit che compongono il dato in uscita. Se, ad esempio, abbiamo un ADC ad otto bit che accetta in ingresso tensioni comprese fra 0 e 5 volt, poiché con 8 bit sono rappresentabili soltanto 28=256 combinazioni diverse, si possono rappresentare soltanto 256 valori diversi di tensioni d’ingresso, valori che differiscono fra loro di un quanto Q pari a 5 volt/256= 19,3 millivolt circa. Ciò significa che una variazione della tensione d’ingresso inferiore al quanto non verrebbe rilevata in uscita. Il quanto viene anche detto intervallo di quantizzazione. Tale intervallo di quantizzazione o errore di quantizzazione può essere minimizzato soltanto aumentando il numero di bit che costituiscono l’uscita dell’ADC.

Supponiamo ora, sempre continuando con il nostro esempio, di fare in modo che il numero prodotto in uscita dall’ADC vari da N ad N+1 quando la tensione di ingresso varia fra N*Q ed (N+1)Q.

Come si può notare, l’errore massimo che si commette, confrontando la tensione quantizzata con la tensione d’ingresso è proprio pari al quanto.

Vediamo ora un secondo esempio in cui facciamo in modo che l’uscita vari da N ad N+1 quando la tensione d’ingresso sia compresa a metà dell’intervallo compreso fra NQ ed (N+1)Q.

come si può verificare dal grafico e dai calcoli effettuati dal foglio elettronico si vede che l’errore massimo che si commette diventa la metà del quanto. Questa è la scelta ottimale, nel senso che permette di minimizzare l’errore di quantizzazione. . poiché con n bit si possono comporre al massimo 2n combinazioni diverse, il numero in uscita può essere al massimo 2n-1 corrispondente ad una tensione quantizzata V=Q*(2n-1). La tensione VFS=Q*2n viene detta tensione di fondo scala. Nella migliore delle ipotesi l’errore di quantizzazione è pari a Q/2=(VFS/2n)/2=VFS/2n+1.

L’errore di quantizzazione si può interpretare come un rumore indesiderato che si sovrappone al nostro segnale d’ingresso. Con una serie di passaggi matematici si trova che il rapporto fra il segnale e questo rumore diventa tanto migliore quanto maggiore è il rapporto fra il valore massimo del segnale ed il valore di fondo scala dell’ADC. Questo deriva dal fatto che un segnale di piccola ampiezza rispetto al valore di fondo scala dell’ADC non ne sfrutta tutta la risoluzione. Se dobbiamo convertire un segnale, quindi, conviene prima amplificarlo in modo da portare il suo valore massimo al massimo valore ammissibile in ingresso all’ADC. Dalla formula matematica che abbiamo tralasciato nonostante sapessimo di poter contare sulle vostre incredibili capacità matematiche universalmente riconosciute, si vede anche che il rapporto segnale-rumore migliora al crescere del numero n dei bit dell’ADC.

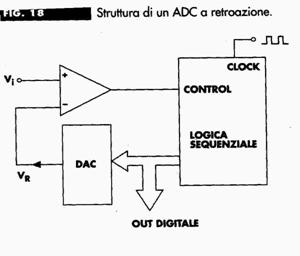

Il principio di funzionamento di un ADC è rappresentato in figura. Il blocco logica sequenziale è un blocco che è in grado di generare tutte le combinazioni possibili degli n bit dell’ADC. Queste sequenze di bit vanno in ingresso ad un DAC che genera la corrispondente tensione in uscita. Appena tale tensione diventa maggiore o uguale a quella di ingresso, l’uscita del comparatore va bassa bloccando il circuito sequenziale e congelando la stringa di bit che si voleva ottenere come risultato della conversione.

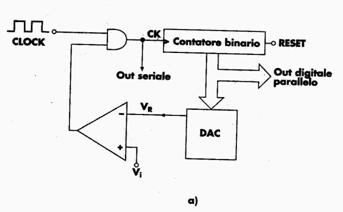

questo è lo schema di principio dei convertitori A/D a retroazione. L’esempio più semplice è il counting ADC o convertitore a conteggio o a gradinata i l cui schema di principio è il seguente

In questo ADC il circuito di logica sequenziale è un contatore binario, pilotato da un clock. Ad ogni impulso di clock il contenuto del contatore binario si aggiorna . il numero contenuto nel contatore passa al DAC. Quando la gradinata prodotta dal DAC raggiunge e supera il valore di tensione Vi, l’uscita del comparatore va a zero per cui blocca a zero l’uscita della porta AND, impedendo al clock di raggiungere il contatore binario. In tal modo l’uscita del contatore binario rimane congelata. Per far partire una nuova conversione occorre resettare il contatore binario mediante il segnale di RESET.

Questo tipo di convertitore presenta come problema fondamentale quello del tempo impiegato per la conversione che è elevato ed inoltre è molto variabile a seconda della tensione da convertire. Infatti tanto più è elevato il valore di tale tensione tanto maggiore sarà il numero di periodi di clock necessari perché l’uscita del DAC giunga a superare la tensione d’ingresso. Per sicurezza chi progetta il circuito in cui è inserito l’ADC, per evitare problemi di sincronizzazione dovrà considerare prudenzialmente il tempo massimo possibile che coincide con il tempo necessario affinché il contatore giunga a contare il numero massimo possibile che è 2n-1.

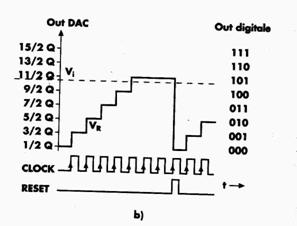

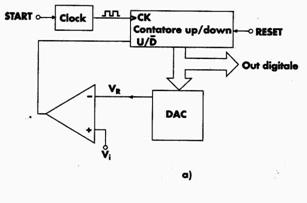

Servo-convertitore o tracking ADC o ADC ad inseguimento.

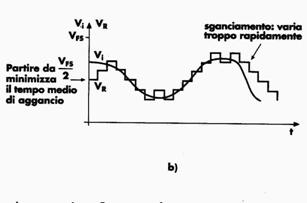

Se il segnale di ingresso diminuisce la sua ampiezza dopo che l’ADC ha portato a termine la sua conversione, il convertitore a gradinata non può modificare la sua uscita per seguire la diminuzione del segnale in ingresso. Per ottenere questa possibilità possiamo modificare lo schema precedente sostituendo al contatore up un contatore up/down facendo in modo che l’uscita del comparatore serva per selezionare la direzione del conteggio (vedi figura)

se la tensione d’ingresso è minore di quella fornita dal DAC, l’uscita del comparatore è a zero per cui il contatore funziona in modalità down e la tensione di uscita del DAC tende a diminuire. Se la tensione da convertire diventa superiore a quella del DAC, l’uscita del comparatore va ad 1 ed il contatore viene impostato in modalità up. Nella figura seguente è mostrato il processo di aggancio

se il convertitore è lasciato libero di inseguire le variazioni della tensione d’ingresso si dice che è in free running. Per questi tipi di convertitori non ha molto senso cercare di stabilire la velocità di conversione . diventa più interessante definire lo slew rate ammissibile in ingresso, cioè la velocità massima di variazione dell’ingresso affinché il convertitore sia ancora in grado di agganciarsi ad essa. Si può dimostrare che lo slew rate massimo è pari al rapporto fra quanto Q e tempo di clock.

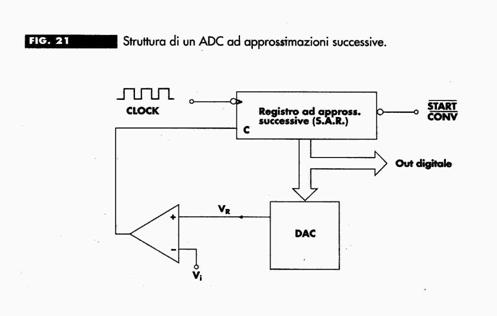

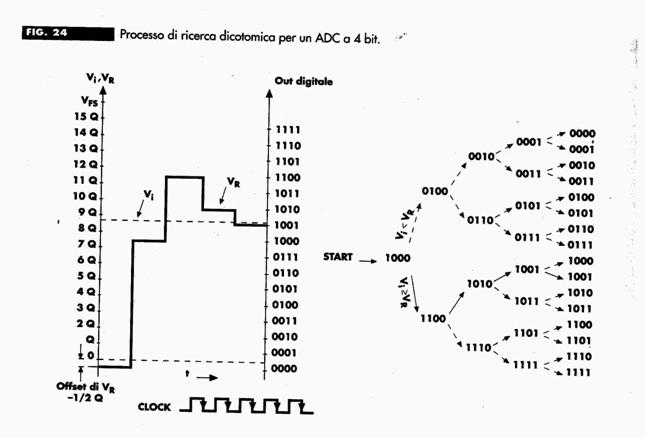

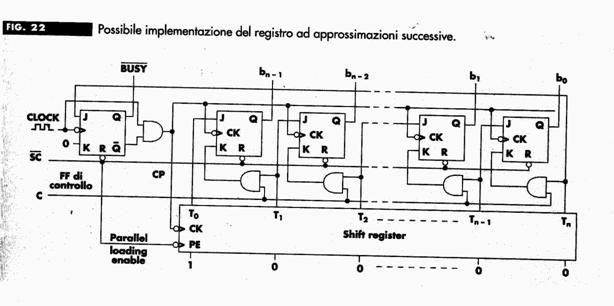

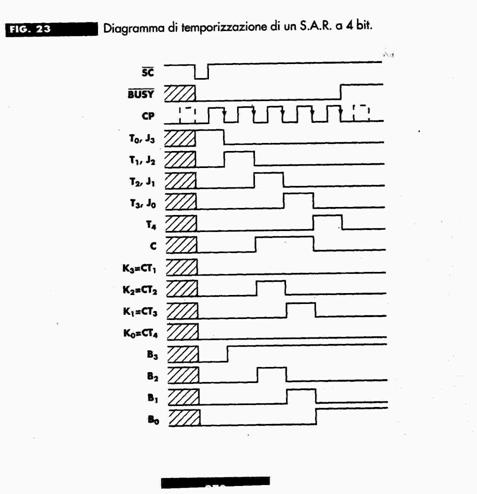

Convertitori ad approssimazioni successive

Questa architettura consente di avere convertitori più veloci e quindi più adatti a sistemi di acquisizione dati basati su microprocessore.

il circuito sequenziale in questo caso è un registro S.A.R. o registro ad approssimazioni successive. Questo registro funziona nella logica della ricerca dicotomica. Applicata al nostro problema questa strategia si può rappresentare nel modo seguente. Noi vogliamo individuare la stringa di bit corrispondente al valore di tensione Vi presente in ingresso. Consideriamo la seguente tabella che mostra le uscite del DAC per un ADC a 8 bit.

|

DECIM |

BINARIO |

TENSIONE |

|

Quanto |

|||||||

|

|

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

|

|

0,019531 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0,01953125 |

|

|

|

2 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0,0390625 |

|

|

|

3 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0,05859375 |

|

|

|

4 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0,078125 |

|

|

|

5 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0,09765625 |

|

|

|

6 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0,1171875 |

|

|

|

7 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0,13671875 |

|

|

|

8 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0,15625 |

|

|

|

9 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0,17578125 |

|

|

|

10 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0,1953125 |

|

|

|

11 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0,21484375 |

|

|

|

12 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0,234375 |

|

|

|

13 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0,25390625 |

|

|

|

14 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0,2734375 |

|

|

|

15 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0,29296875 |

|

|

|

16 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0,3125 |

|

|

|

17 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0,33203125 |

|

|

|

18 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0,3515625 |

|

|

|

19 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0,37109375 |

|

|

|

20 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0,390625 |

|

|

|

21 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0,41015625 |

|

|

|

22 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0,4296875 |

|

|

|

23 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0,44921875 |

|

|

|

24 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0,46875 |

|

|

|

25 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0,48828125 |

|

|

|

26 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0,5078125 |

|

|

|

27 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0,52734375 |

|

|

|

28 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0,546875 |

|

|

|

29 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0,56640625 |

|

|

|

30 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0,5859375 |

|

|

|

31 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0,60546875 |

|

|

|

32 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0,625 |

|

|

|

33 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0,64453125 |

|

|

|

34 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0,6640625 |

|

|

|

35 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0,68359375 |

|

|

|

36 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0,703125 |

|

|

|

37 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0,72265625 |

|

|

|

38 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0,7421875 |

|

|

|

39 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0,76171875 |

|

|

|

40 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0,78125 |

|

|

|

41 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0,80078125 |

|

|

|

42 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0,8203125 |

|

|

|

43 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0,83984375 |

|

|

|

44 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0,859375 |

|

|

|

45 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0,87890625 |

|

|

|

46 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0,8984375 |

|

|

|

47 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0,91796875 |

|

|

|

48 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0,9375 |

|

|

|

49 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0,95703125 |

|

|

|

50 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0,9765625 |

|

|

|

51 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0,99609375 |

|

|

|

52 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1,015625 |

|

|

|

53 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1,03515625 |

|

|

|

54 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1,0546875 |

|

|

|

55 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1,07421875 |

|

|

|

56 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1,09375 |

|

|

|

57 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1,11328125 |

|

|

|

58 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1,1328125 |

|

|

|

59 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1,15234375 |

|

|

|

60 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1,171875 |

|

|

|

61 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1,19140625 |

|

|

|

62 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1,2109375 |

|

|

|

63 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1,23046875 |

|

|

|

64 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1,25 |

|

|

|

65 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1,26953125 |

|

|

|

66 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1,2890625 |

|

|

|

67 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1,30859375 |

|

|

|

68 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1,328125 |

|

|

|

69 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1,34765625 |

|

|

|

70 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1,3671875 |

|

|

|

71 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1,38671875 |

|

|

|

72 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1,40625 |

|

|

|

73 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1,42578125 |

|

|

|

74 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1,4453125 |

|

|

|

75 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1,46484375 |

|

|

|

76 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1,484375 |

|

|

|

77 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1,50390625 |

|

|

|

78 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1,5234375 |

|

|

|

79 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1,54296875 |

|

|

|

80 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1,5625 |

|

|

|

81 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1,58203125 |

|

|

|

82 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1,6015625 |

|

|

|

83 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1,62109375 |

|

|

|

84 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1,640625 |

|

|

|

85 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1,66015625 |

|

|

|

86 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1,6796875 |

|

|

|

87 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1,69921875 |

|

|

|

88 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1,71875 |

|

|

|

89 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1,73828125 |

|

|

|

90 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1,7578125 |

|

|

|

91 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1,77734375 |

|

|

|

92 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1,796875 |

|

|

|

93 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1,81640625 |

|

|

|

94 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1,8359375 |

|

|

|

95 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1,85546875 |

|

|

|

96 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1,875 |

|

|

|

97 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1,89453125 |

|

|

|

98 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1,9140625 |

|

|

|

99 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1,93359375 |

|

|

|

100 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1,953125 |

|

|

|

101 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1,97265625 |

|

|

|

102 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1,9921875 |

|

|

|

103 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

2,01171875 |

|

|

|

104 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

2,03125 |

|

|

|

105 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

2,05078125 |

|

|

|

106 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

2,0703125 |

|

|

|

107 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

2,08984375 |

|

|

|

108 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

2,109375 |

|

|

|

109 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

2,12890625 |

|

|

|

110 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

2,1484375 |

|

|

|

111 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

2,16796875 |

|

|

|

112 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

2,1875 |

|

|

|

113 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

2,20703125 |

|

|

|

114 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

2,2265625 |

|

|

|

115 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

2,24609375 |

|

|

|

116 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

2,265625 |

|

|

|

117 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

2,28515625 |

|

|

|

118 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

2,3046875 |

|

|

|

119 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

2,32421875 |

|

|

|

120 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

2,34375 |

|

|

|

121 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

2,36328125 |

|

|

|

122 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

2,3828125 |

|

|

|

123 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

2,40234375 |

|

|

|

124 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

2,421875 |

|

|

|

125 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

2,44140625 |

|

|

|

126 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

2,4609375 |

|

|

|

127 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

2,48046875 |

|

|

|

128 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2,5 |

|

|

|

129 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

2,51953125 |

|

|

|

130 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

2,5390625 |

|

|

|

131 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

2,55859375 |

|

|

|

132 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

2,578125 |

|

|

|

133 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

2,59765625 |

|

|

|

134 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

2,6171875 |

|

|

|

135 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

2,63671875 |

|

|

|

136 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

2,65625 |

|

|

|

137 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

2,67578125 |

|

|

|

138 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

2,6953125 |

|

|

|

139 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

2,71484375 |

|

|

|

140 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

2,734375 |

|

|

|

141 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

2,75390625 |

|

|

|

142 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

2,7734375 |

|

|

|

143 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

2,79296875 |

|

|

|

144 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

2,8125 |

|

|

|

145 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2,83203125 |

|

|

|

146 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

2,8515625 |

|

|

|

147 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

2,87109375 |

|

|

|

148 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

2,890625 |

|

|

|

149 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

2,91015625 |

|

|

|

150 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

2,9296875 |

|

|

|

151 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

2,94921875 |

|

|

|

152 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

2,96875 |

|

|

|

153 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

2,98828125 |

|

|

|

154 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

3,0078125 |

|

|

|

155 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

3,02734375 |

|

|

|

156 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

3,046875 |

|

|

|

157 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

3,06640625 |

|

|

|

158 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

3,0859375 |

|

|

|

159 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

3,10546875 |

|

|

|

160 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

3,125 |

|

|

|

161 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

3,14453125 |

|

|

|

162 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

3,1640625 |

|

|

|

163 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

3,18359375 |

|

|

|

164 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

3,203125 |

|

|

|

165 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

3,22265625 |

|

|

|

166 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

3,2421875 |

|

|

|

167 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

3,26171875 |

|

|

|

168 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

3,28125 |

|

|

|

169 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

3,30078125 |

|

|

|

170 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

3,3203125 |

|

|

|

171 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

3,33984375 |

|

|

|

172 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

3,359375 |

|

|

|

173 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

3,37890625 |

|

|

|

174 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

3,3984375 |

|

|

|

175 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

3,41796875 |

|

|

|

176 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

3,4375 |

|

|

|

177 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

3,45703125 |

|

|

|

178 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

3,4765625 |

|

|

|

179 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

3,49609375 |

|

|

|

180 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

3,515625 |

|

|

|

181 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

3,53515625 |

|

|

|

182 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

3,5546875 |

|

|

|

183 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

3,57421875 |

|

|

|

184 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

3,59375 |

|

|

|

185 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

3,61328125 |

|

|

|

186 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

3,6328125 |

|

|

|

187 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

3,65234375 |

|

|

|

188 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

3,671875 |

|

|

|

189 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

3,69140625 |

|

|

|

190 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

3,7109375 |

|

|

|

191 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

3,73046875 |

|

|

|

192 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

3,75 |

|

|

|

193 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

3,76953125 |

|

|

|

194 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

3,7890625 |

|

|

|

195 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

3,80859375 |

|

|

|

196 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

3,828125 |

|

|

|

197 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

3,84765625 |

|

|

|

198 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

3,8671875 |

|

|

|

199 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

3,88671875 |

|

|

|

200 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

3,90625 |

|

|

|

201 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

3,92578125 |

|

|

|

202 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

3,9453125 |

|

|

|

203 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

3,96484375 |

|

|

|

204 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

3,984375 |

|

|

|

205 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

4,00390625 |

|

|

|

206 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

4,0234375 |

|

|

|

207 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

4,04296875 |

|

|

|

208 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

4,0625 |

|

|

|

209 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

4,08203125 |

|

|

|

210 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

4,1015625 |

|

|

|

211 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

4,12109375 |

|

|

|

212 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

4,140625 |

|

|

|

213 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

4,16015625 |

|

|

|

214 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

4,1796875 |

|

|

|

215 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

4,19921875 |

|

|

|

216 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

4,21875 |

|

|

|

217 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

4,23828125 |

|

|

|

218 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

4,2578125 |

|

|

|

219 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

4,27734375 |

|

|

|

220 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

4,296875 |

|

|

|

221 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

4,31640625 |

|

|

|

222 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

4,3359375 |

|

|

|

223 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

4,35546875 |

|

|

|

224 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

4,375 |

|

|

|

225 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

4,39453125 |

|

|

|

226 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

4,4140625 |

|

|

|

227 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

4,43359375 |

|

|

|

228 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

4,453125 |

|

|

|

229 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

4,47265625 |

|

|

|

230 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

4,4921875 |

|

|

|

231 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

4,51171875 |

|

|

|

232 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

4,53125 |

|

|

|

233 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

4,55078125 |

|

|

|

234 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

4,5703125 |

|

|

|

235 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

4,58984375 |

|

|

|

236 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

4,609375 |

|

|

|

237 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

4,62890625 |

|

|

|

238 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

4,6484375 |

|

|

|

239 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

4,66796875 |

|

|

|

240 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

4,6875 |

|

|

|

241 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

4,70703125 |

|

|

|

242 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

4,7265625 |

|

|

|

243 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

4,74609375 |

|

|

|

244 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

4,765625 |

|

|

|

245 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

4,78515625 |

|

|

|

246 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

4,8046875 |

|

|

|

247 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

4,82421875 |

|

|

|

248 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

4,84375 |

|

|

|

249 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

4,86328125 |

|

|

|

250 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

4,8828125 |

|

|

|

251 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

4,90234375 |

|

|

|

252 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

4,921875 |

|

|

|

253 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

4,94140625 |

|

|

|

254 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

4,9609375 |

|

|

|

255 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

4,98046875 |

|

|

Data la tensione Vi d’ingresso si cerca di stabilire

innanzitutto se il bit più significativo deve stare a 1 o a zero. Si pone il

bit più significativo ad 1 e tutti gli altri bit a zero. Il DAC darà la

tensione corrispondente e il comparatore confronterà le due tensioni. Se la

tensione di uscita del DAC supera la tensione di ingresso da convertire il

comparatore porta la sua uscita d 1 costringendo il SAR a porre l’MSB a 0. se

la tensione di uscita del DAC è inferiore a quella di ingresso da convertire,

il comparatore pone la sua uscita ad 1 lasciano il MSB del SAR ad