P10 - Scheda RAM con DMA

Specifiche di progetto

La scheda realizza un banco di memoria RAM da 2 Kbyte, interfacciabile con la scheda CPU Z80.

Il banco di memoria deve poter essere posizionato agli indirizzi a partire da 0000h, oppure a partire da 8000h a scelta dell’utente.

La scheda deve poter operare in modalità DMA, limitatamente alle prime 256 locazioni (deve in pratica essere possibile inserire direttamente dei dati in queste locazioni bypassando il microprocessore).

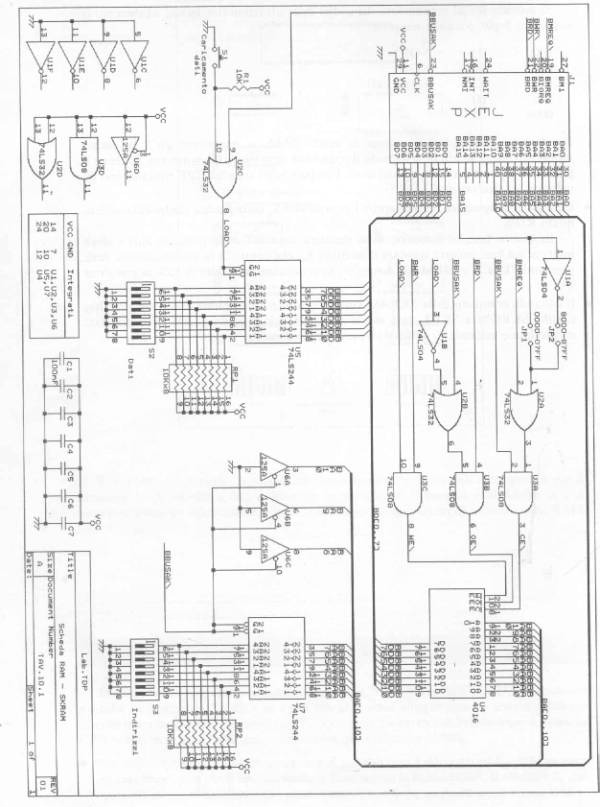

Nella figura seguente vi è lo schema del progetto.

Circuito d’indirizzamento.

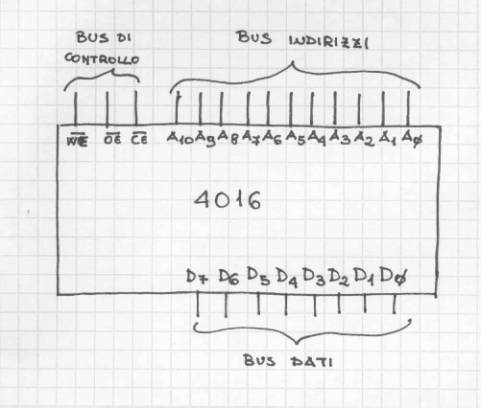

Il chip di memoria utilizzato è il 4016. Avendo una capacità

di 2048 locazioni di memoria esso necessita di 11 ingressi d’indirizzamento (211=2048),

da A0 a A10.

e di 8 piedini per l’interfacciamento con il bus dati. Sono presenti, inoltre, il chip enable CE, un segnale di abilitazione WE per abilitare le operazioni di scrittura sulle locazioni del chip e un segnale OE (output enable) per abilitare le operazioni di lettura del contenuto delle locazioni.

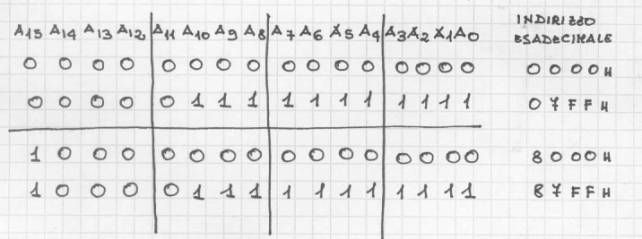

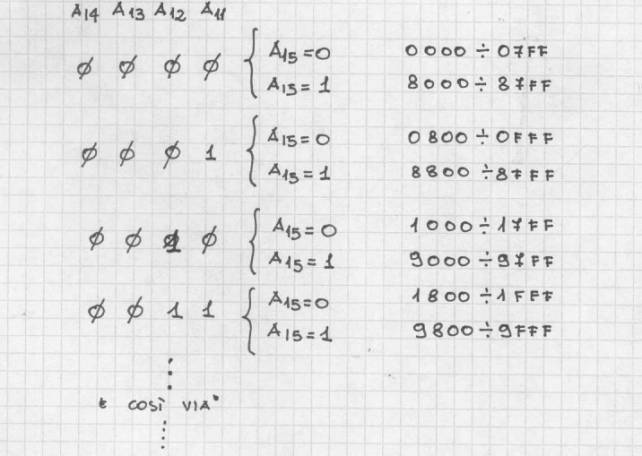

Effettuiamo l’analisi degli indirizzi. Come si vede dalla tabella seguente

nel caso si voglia posizionare il chip alle locazioni 0000-07FF, si ha A15 = 0, mentre, nel caso si posizioni il chip alle locazioni 8000 – 87FF, si ha A15 0 1. in ogni caso, i bit A11 – A14 sono a zero.

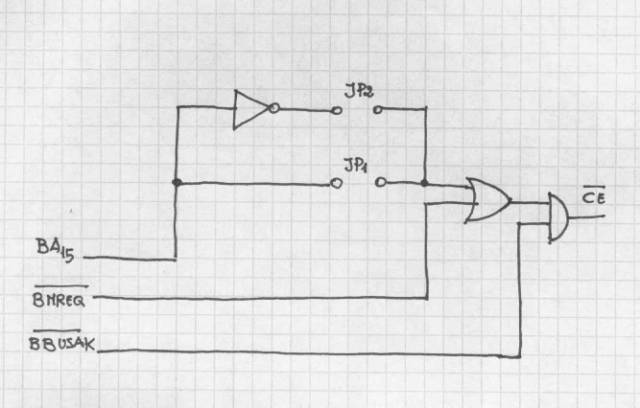

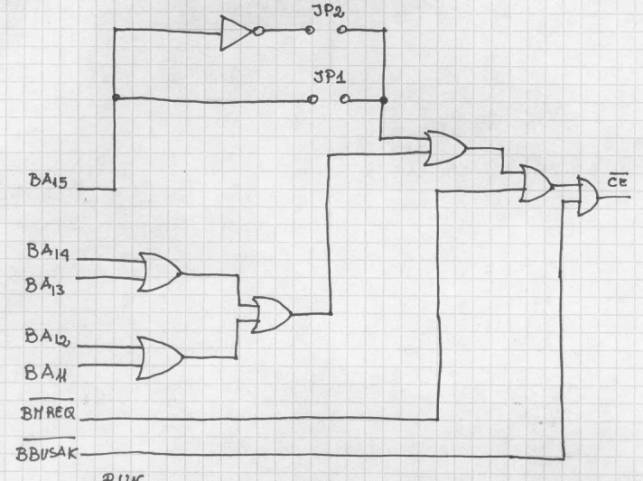

Come si può vedere dallo schema, la soluzione adottata prevede che i bit A11 – A14 non vengono utilizzati dal circuito di decodifica degli indirizzi, mentre il chip di memoria viene abilitato dal seguente circuito.

se si vuole che il chip sia posizionato agli indirizzi 0000 – 07FF, si deve effettuare un collegamento sul ponticello JP1, in modo che, se A15 = 0 e MREQ = 0, l’uscita della OR sia a zero così come l’uscita della AND, per cui il segnale CE è uguale a zero e il chip è abilitato. Se, invece, il chip va posizionato agli indirizzi 8000 – 87FF, si effettua il collegamento sul ponticello JP2. in questo caso, se A15 = 1, passa attraverso la NOT, per cui gli ingressi della OR sono entrambi a zero e si abilita il chip. Come si può notare, all’ingresso della AND arriva anche il segnale BUSAK di modo che, se la scheda funziona in modalità DMA, il microprocessore è sconnesso dal bus, ma BUSAK = 0 per cui il chip è abilitato comunque, e si possono inserire dati nelle sue locazioni in modalità manuale.

Poiché A11 – A14 non vengono utilizzati, si parla di decodifica parziale degli indirizzi. In questo caso, in realtà, gli indirizzi dei chip non sono univoci. Come si nota dalla tabella seguente, in funzione del valore di questi bit che non sono presi in considerazione dal circuito di abilitazione, il chip verrebbe abilitato anche se, sul bus dati ci fossero i seguenti indirizzi

In realtà, anche se A11 – A14 non sono tutti a zero, il chip viene abilitato. Per fissare in modo univoco gli indirizzi del chip bisogna effettuare una decodifica totale per essere sicuri che A11 – A14 siano sicuramente a zero.

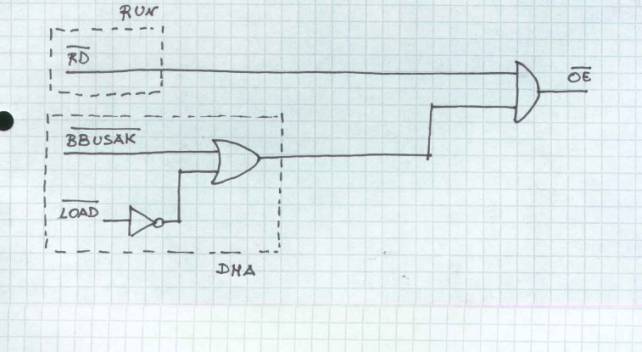

Generazione di Output Enable.

L’abilitazione in lettura del chip avviene attraverso il segnale RD del microprocessore se siamo in modalità RUN, cioè il microprocessore ha il controllo della scheda.

Il segnale LOAD è un segnale prodotto nella parte bassa del circuito

|

LOAD |

0 |

Stiamo caricando dati nel chip in modalità DMA |

|

1 |

Siamo in modalità DMA ma non stiamo caricando dati nel chip di memoria |

Quindi, per abilitare in lettura il chip, deve essere BUSAK = 0e LOAD = 1 (dopo la NOT abbiamo uno zero); a questo punto i due ingressi della OR sono entrambi a zero, l’uscita della OR è zero, così come l’uscita della AND.

Generazione di Write Enable.

IL WE viene generato o attraverso il WR del microprocessore o attraverso il LOAD = 0. L’uscita della AND, infatti, sarà a zero se almeno uno degli ingressi sarà a zero.

Selezione degli indirizzi in modalità DMA.

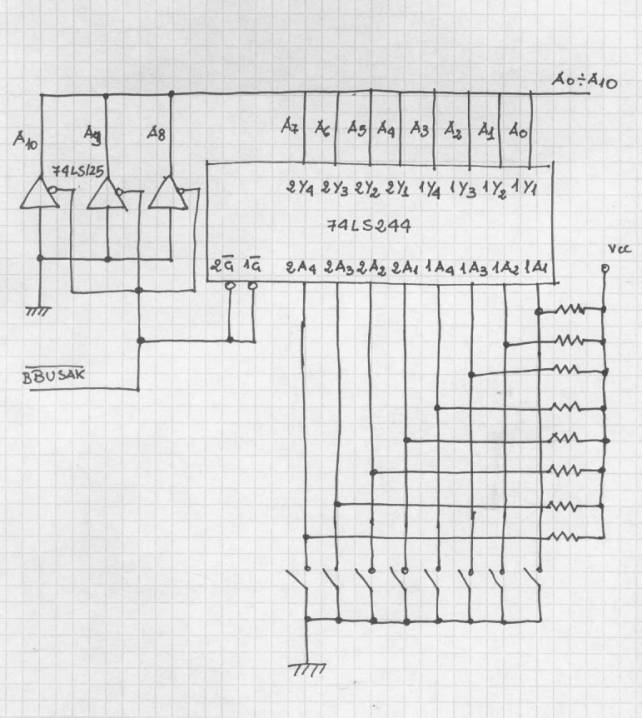

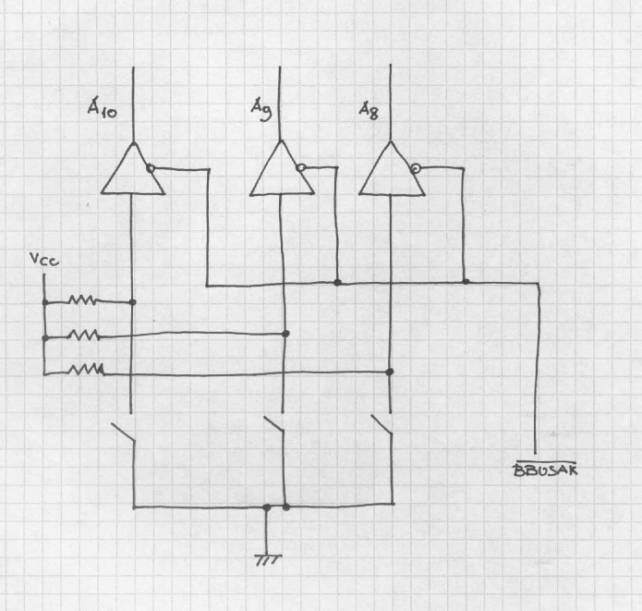

Quando siamo in modalità DMA, il microprocessore è sconnesso dal bus, per cui dal connettore JEXP non arrivano segnali di indirizzo che vengono impostati manualmente dal seguente circuito.

I valori dei bit vengono impostati aprendo e chiudendo gli interruttori. Se un interruttore è chiuso la linea corrispondente va a massa; se l’interruttore è chiuso, la resistenza porta la linea a livello alto.

In questo caso il buffer serve per isolare gli interruttori dal bus in modo che la loro posizione influenzi lo stato del bus indirizzi soltanto quando il buffer è abilitato. Poiché vogliamo che il buffer sia abilitato soltanto in modalità DMA, l’abilitazione è ricavata da BUSAK. Si noti che i bit A10, A9 e A8, quando le porte buffer sono abilitate, vanno a massa, per cui, in modalità DMA possono essere selezionate soltanto le prime 256 locazioni da

000|0000|0000 = 000H a 000|1111|1111 = 0FFH

E’ facile espandere il progetto in modo da poter accedere in modalità DMA a tutte le locazioni del chip; infatti, basta che i bit A10, A9 e A8 non vengano collegati attraverso le porte buffer, direttamente a massa, ma ad altri interruttori

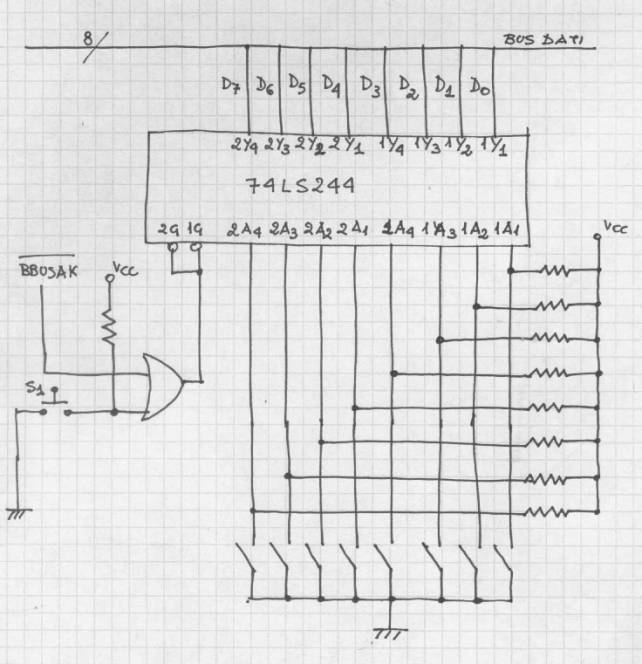

Una volta indirizzata la locazione che ci interessa modificare, occorre anche impostare il suo contenuto e questo avviene in modo analogo con altri 8 interruttori collegati attraverso un buffer al bus dati.

Come si può notare, l’abilitazione del buffer è ricavata dal segnale LOAD cui si accennava prima. Si noti come LOAD sia ricavata essenzialmente chiudendo l’interruttore S1. tuttavia la linea così realizzata, è messa in ingresso ad una Or alla quale va anche BUSAK. In questo modo si è sicuri che il buffer sia collegato al bus dati solo se stiamo in modalità DMA. In caso contrario potrebbe accadere che noi poniamo LOAD a zero, facendo così collegare gli interruttori al bus dati, mentre, nella scheda principale il microprocessore non è sconnesso dal bus, per cui si avrebbe un conflitto sulle linee dati.